News

IC design challenges

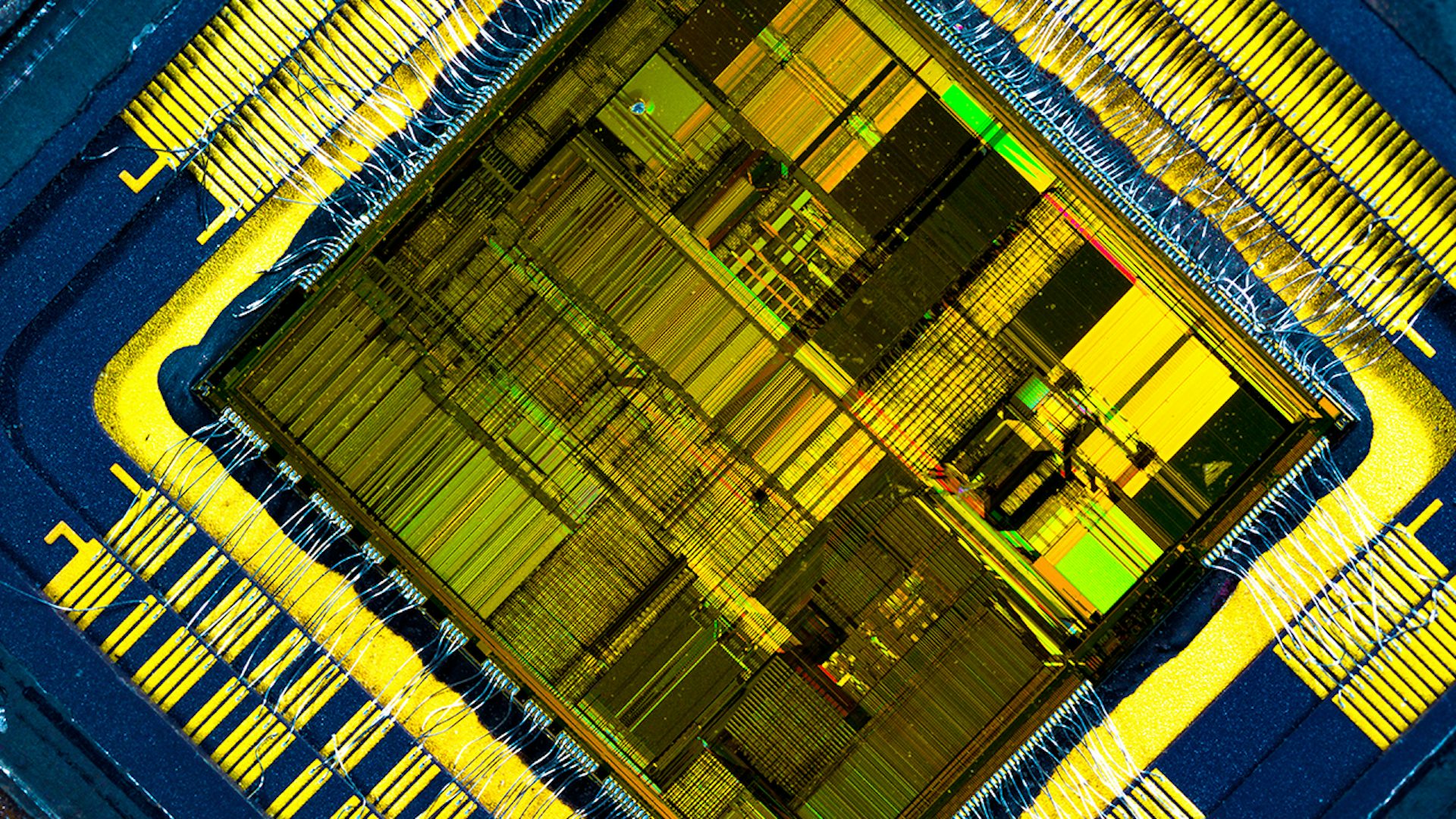

Every new IC process node introduces a new set of design complexities. To ensure you can meet performance, power, and area requirements and deliver IC innovations on time requires a comprehensive tool flow that spans from C-level, high-level synthesis, all the way to signoff verification.

Conquer IC design challenges

Meeting performance, power and area requirements while still delivering IC innovations on time requires a comprehensive tool flow spanning from C-level design, all the way to signoff verification.

Learn moreIC verification & validation challenges

IC verification can account for up to seventy percent of the IC design cycle. In today's connected world, design teams not only have to ensure their designs are functionally correct, but they also need the means to validate and test their ICs in the context of the entire end-system.

Conquer IC verification & validation challenges

Leading verification teams not only have to ensure their designs are functionally correct, they must also validate and test their ICs in the context of the entire end-system.

Learn More