How process engineering software helps your business

Simplify the delivery of high-quality, consistent SMT process collateral. Efficiently meet the process engineering demands of high-mix, low-volume production.

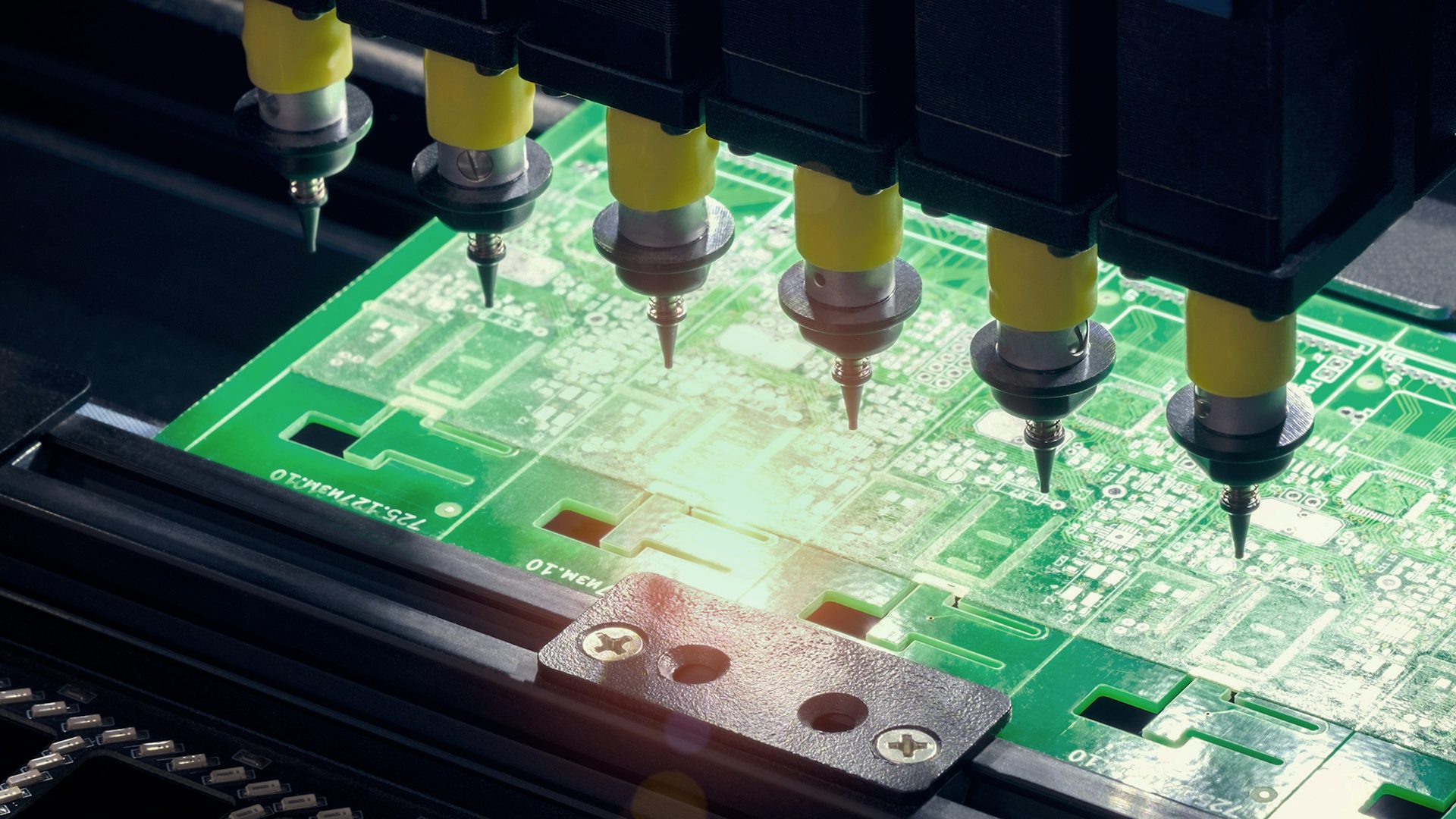

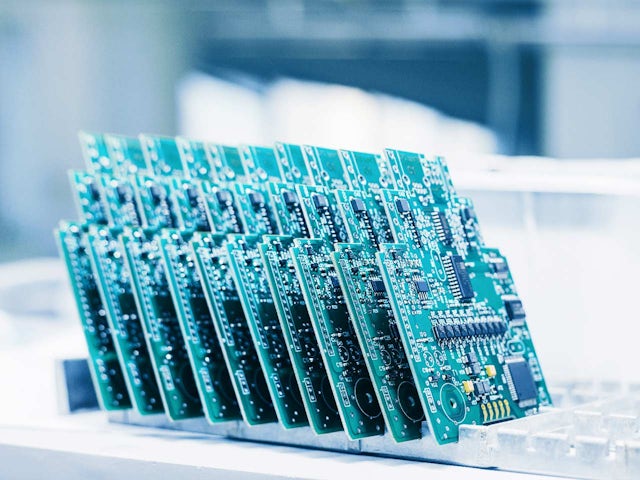

Process preparation for PCB assembly and test

Valor Process Preparation creates a central database of all manufacturing process definitions and engineering data. This provides flexibility to move between machine vendors and manufacturing sites. Acting as a single environment for all manufacturing stages, this SMT programming tool ensures data is constantly up to date, and manufacturing is error-free.

Accurate and efficient PCB quoting

Electronic manufacturing services (EMS) companies often provide quotes for projects that never make it into production. Valor BOM Connector reduces the time it takes to create accurate quotations for printed circuit board (PCB) assemblies. This minimizes the waste of valuable engineering hours.

ESCATEC

Global electronics contract manufacturer reduces re-spin time by at least 96 percent

Company:ESCATEC

Industry:Electronics, Semiconductor devices

Location:Penang, Malaysia

Siemens Software:Valor Parts Library, Valor Process Preparation

Explore related product

Get a single environment for manufacturing process engineering of all PCB assembly stages. Data is constantly up to date for an error-free manufacturing process.