Electronic System Level Design

Vista Flow

The Vista Flow consists of the steps typically used by SoC architects, hardware engineers, and software engineers to create TLM Models, assemble and configure the system, simulate, verify and debug, analyze and optimize performance, and power and integrate with the software.

Get in touch with our sales team 1-800-547-3000

Prototyping, debugging, and analyzing complex systems

ESL design methodology allows engineers to perform design optimizations on today's advanced designs more quickly, efficiently, and cost-effectively by prototyping, debugging, and analyzing complex systems before the RTL stage. ESL and RTL methodology leads to a continuation of the design cycle.

Quickly explore complex micro-architecture alternatives

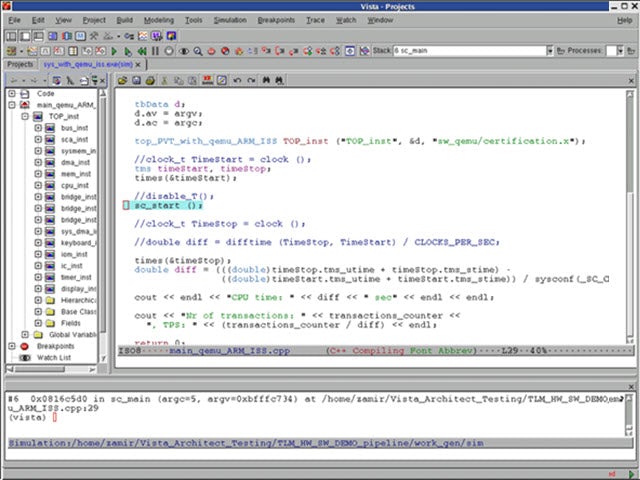

Vista Model Builder automates the functionality modeling with a set of TLM classes and convenience layer for more efficient and guided behavioral modeling. A TLM code skeleton is automatically derived/generated from a set of ports, registers, and memory declarations, generating compact SystemC source code compliant with TLM 2.0, so users can then model the internal behavior only on their own.

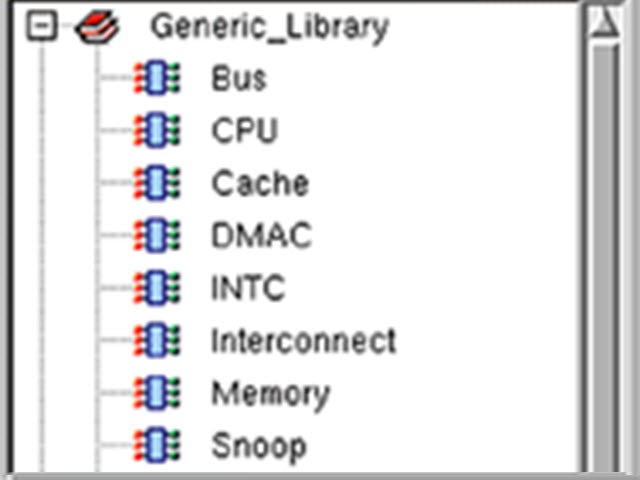

Vista Architect Environment

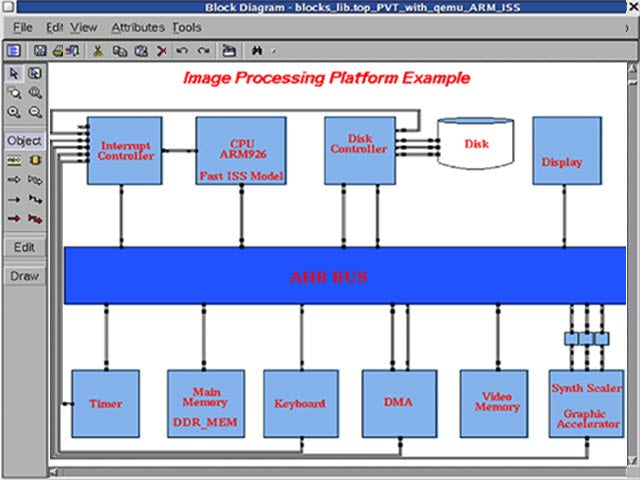

Vista Architect offers a set of fast generic models for initial platform assembly and early validation. All models are TLM 2.0 compliant and can be instantiated as building blocks through a text-based format or a block diagram format for assembling any target platform.

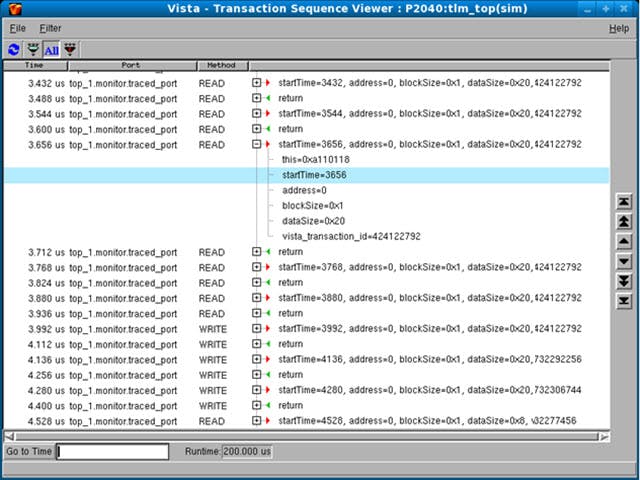

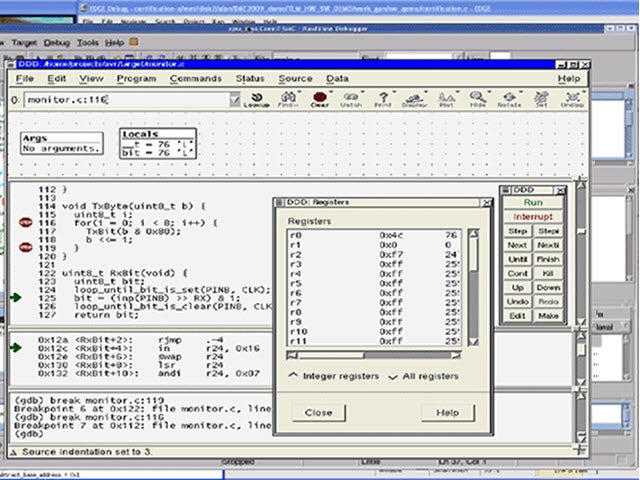

Verify and Debug the System

Vista Architect offers the industry's most advanced SystemC debug toolset (Vista Debug) designed to validate and debug SystemC TLM platforms. At the architecture level, verification is focused on validating the correct interaction among various IPs and the appropriate flow of data. Vista Architect presents an innovative debugging and tracing concept that focuses on high-level system debug and data flow analysis.

Assemble and Configure the System

During the architecture design phase, models can be intuitively instantiated and assembled into various architecture configurations, interconnect layering, and memory hierarchies. Vista's powerful block diagram editor provides an intuitive graphical platform assembly, editing, and visualization. Vista's text editor assembling mechanism enables users to connect their platform in a text-based form.

Integrate with Software

Users can test and debug the hardware that is driven by software or produce a virtual platform to run firmware, operating systems, or hardware-dependent software applications.

Vista is integrated with Codebench Virtual Edition that provides the capability to display HW and SW traces together on one timeline to reveal how software execution affects the behavior of the hardware.

Quickly Change the Micro-architecture

Vista Architect offers a powerful analysis and reporting toolset that allows users to intuitively analyze different performance and power metrics by looking at load peaks, average latencies, throughput, and utilization on any port, bus, or sub-system without any manual instrumentation.

Create TLM models, debug, optimize, and more

- Architecture design and exploration

- Allow hardware / software tradeoffs analysis

- Early assessment of performance and power

- Virtual platform for software integration and validation

- Reference modeling for RTL verification

- Minimizes risks and maximizes quality of results

Ready to talk to someone today?

We're standing by to answer your questions.

Get in touch with our sales team 1-800-547-3000 or 1-503-685-8000

Verification Academy

Verification Academy provides the skills necessary to mature an organization's functional verification process capabilities, providing a methodological bridge between high-level value propositions and the low-level details.

Verification Horizons blog

Insight and updates on concepts, values, standards, methodologies, and examples to assist with the understanding of what advanced functional verification technologies can do and how to most effectively apply them.

Verification Horizons

The Verification Horizons publication provides concepts, values, methodologies and examples to assist with the understanding of what advanced functional verification technologies can do and how to most effectively apply them.