Veloce Hardware-Assisted Verification Platform

The Veloce hardware-assisted verification platform is a comprehensive and full-featured platform comprised of hardware for emulation and prototyping as well as virtual/hybrid capabilities for early software-driven verification.

Veloce Hardware-assisted Verification System

The Veloce Hardware-assisted verification system is made up of four key components: The Veloce Strato hardware and software platform, Veloce Apps, Veloce Protocol Solutions, and the Veloce FPGA prototyping hardware and software platform.

Learn more

Veloce HW-assisted verification resources

Learn about Veloce Strato+

Vijay Chobisa introduces Veloce Strato+

HAV launch video about Veloce Strato+ by Vijay Chobisa

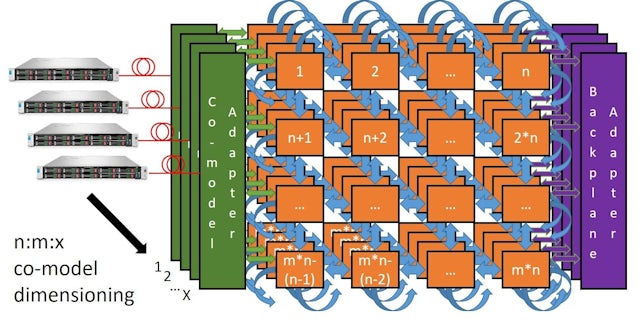

Co-modeling in Veloce

This paper explores how emulation co-modeling, in Veloce is architected to meet the needs of advanced verification and validation.