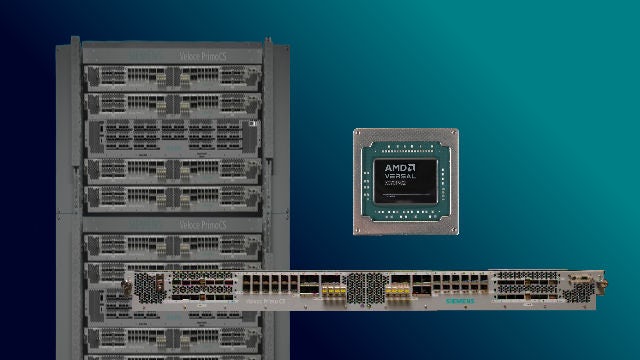

Veloce CS System

Veloce CS is the leading hardware software and system validation platform, including the Veloce Strato CS emulation platform, Veloce Primo CS enterprise prototyping platform, and Veloce proFPGA CS software prototyping platform meeting the demands of complex chips, software, and systems.

Veloce CS System Platform

Veloce CS System hardware and software is constructed for congruency among these platforms for the highest productivity and flexibility for our customers. Veloce OS software, Veloce Solutions and Veloce Apps enables flexibility for customers to easily move between these platforms per their needs.

Answering the Challenges of Advanced IC Development

Today's SoCs contain more logic density, high-speed serial data communications, and multiple logic processors. This increased complexity requires visibility into the hardware, software, and systems integration to understand subtle problems that can occur during silicon and system bring-up.

Congruency

By the virtue of the exact same Veloce hardware and Veloce software architecture, The Veloce CS System offers a highly congruence environment for hardware, software and system verification and validation teams. By enabling exact same Veloce solutions and applications, users have flexibility to move environments from one platform to another with minimal efforts to get the highest productivity.

Performance and Capacity

The Veloce CS System exploits the blade interconnect technology and optical interconnect, delivering the fastest performance with highest scalability. Emulation and enterprise prototyping platforms scale from 40MG to 40+BG and software prototype platform from single FPGA to 12 BG multi blade system.

Software Rising

Software development and validation is the bottleneck in today’s system design flow across all industries. Up until now the software had to wait for RTL verification to be completed. The Veloce CS System pulls the software development cycle in earlier, verifying application software, enabling power/performance analysis at system level, and benchmarking the entire system in a targeted application environment.

Configurability

The Veloce CS System allows multiple teams of RTL designers and software users simultaneous access to a scalable system with heterogeneous workloads placement flexibility. It is an on-demand, instantly reconfigurable platform to support different size designs, use modes, and workloads to maximize the utilization of the system; and comes with placement software to maximize productivity.