Overview

Calibre CMPAnalyzer

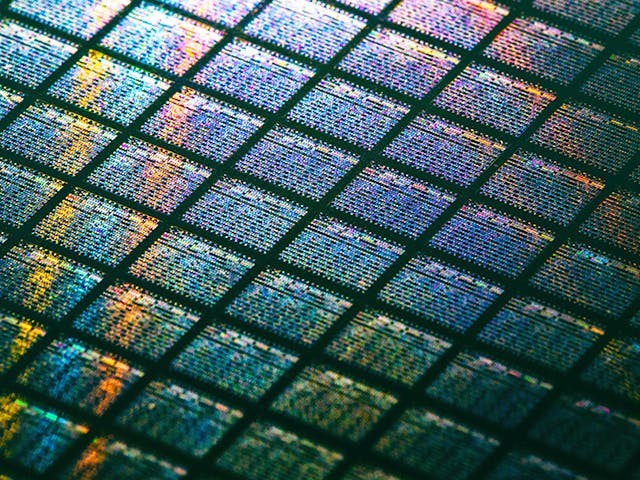

Planarity variation creates hotspots that impact both chip manufacturability and the electrical performance of the design. The Calibre CMPAnalyzer tool examines a layout and simulates the thickness of each layer to enable designers to intelligently modify the design to reduce variation effects.

Get in touch with our technical team: 1-800-547-3000

Comprehensive design analysis for optimization

The Calibre CMPAnalyzer tool lets designers use simulation results to visually highlight and examine a variety of CMP effects. Designers can examine these results layer by layer, and for selected areas in the layout. They can also review specified CMP hotspot checks, such as depth of focus checks.

Automatically determines optimum filling strategy

Using thickness simulation data from the simulator, the Calibre CMPAnalyzer tool determines the optimum filling strategy and passes the information to the Calibre YieldEnhancer tool. The combination of accurate simulation data and the innovative Calibre fill algorithm improves parametric yield while minimizing the added capacitance.

Visual display of CMP impacts speeds analysis

Data provided by CMP simulators to the Calibre CMPAnalyzer tool enable designers to visually highlight and examine a variety of CMP effects. Designers can examine these results layer by layer, and for selected areas in the layout. They can also review specified CMP hotspot checks, such as depth of focus checks.

Integrated for improved modeling

The Calibre CMPAnalyzer tool integrates with Calibre xRC parasitic extraction to create a comprehensive 3D model of the interconnect parameters that more closely matches silicon results. The Calibre xRC tool accurately accounts for the thickness variation across the design, letting designers use this information to validate timing.

Ready to learn more about Calibre?

We're standing by to answer your questions! Get in touch with our team today:

Call: 1-800-547-3000

EDA consulting

Helping you achieve maximum business impact by addressing complex technology and enterprise challenges with a unique blend of development and design experience and methodology expertise.

Support Center

The Siemens Support Center provides you with everything in one easy-to-use location – knowledgebase, product updates, documentation, support cases, license/order information, and more.

Design with Calibre blog

Across all process nodes and design styles, the Calibre toolsuite delivers accurate, efficient, comprehensive IC verification and optimization, while minimizing resource usage and tapeout schedules.