- Home

- Siemens EDA Software

- IC Tool Portfolio

Engineer a Smarter Future Faster

IC design, verification & manufacturing

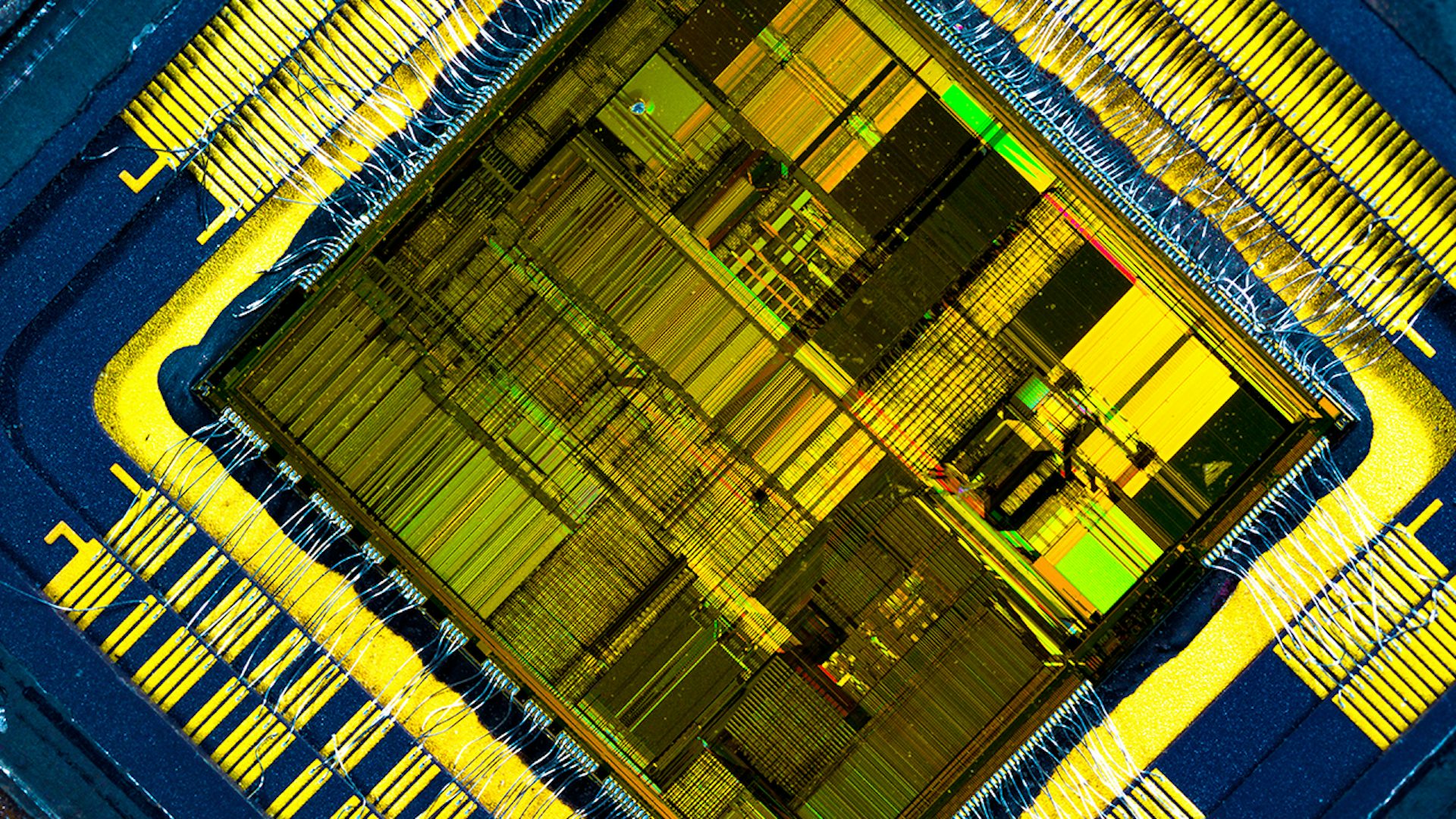

Siemens EDA is a leader in IC design, verification, and manufacturing. Our tools enable customers to design the innovative ICs that drive digitalization worldwide, proliferating high-speed wired and 5G communications, cloud computing, autonomous driving, and AI-smarter everything.

Siemens EDA IC technical resources

Read the latest white papers, datasheets, customer success stories and more.