Engineer a smarter future faster with Siemens EDA

For over 175 years, Siemens has helped customers innovate products and industries. With Siemens EDA and the Siemens Xcelerator portfolio, we enable customers to embrace digital transformation to accelerate the pace of innovation.

Engineer a smarter future faster

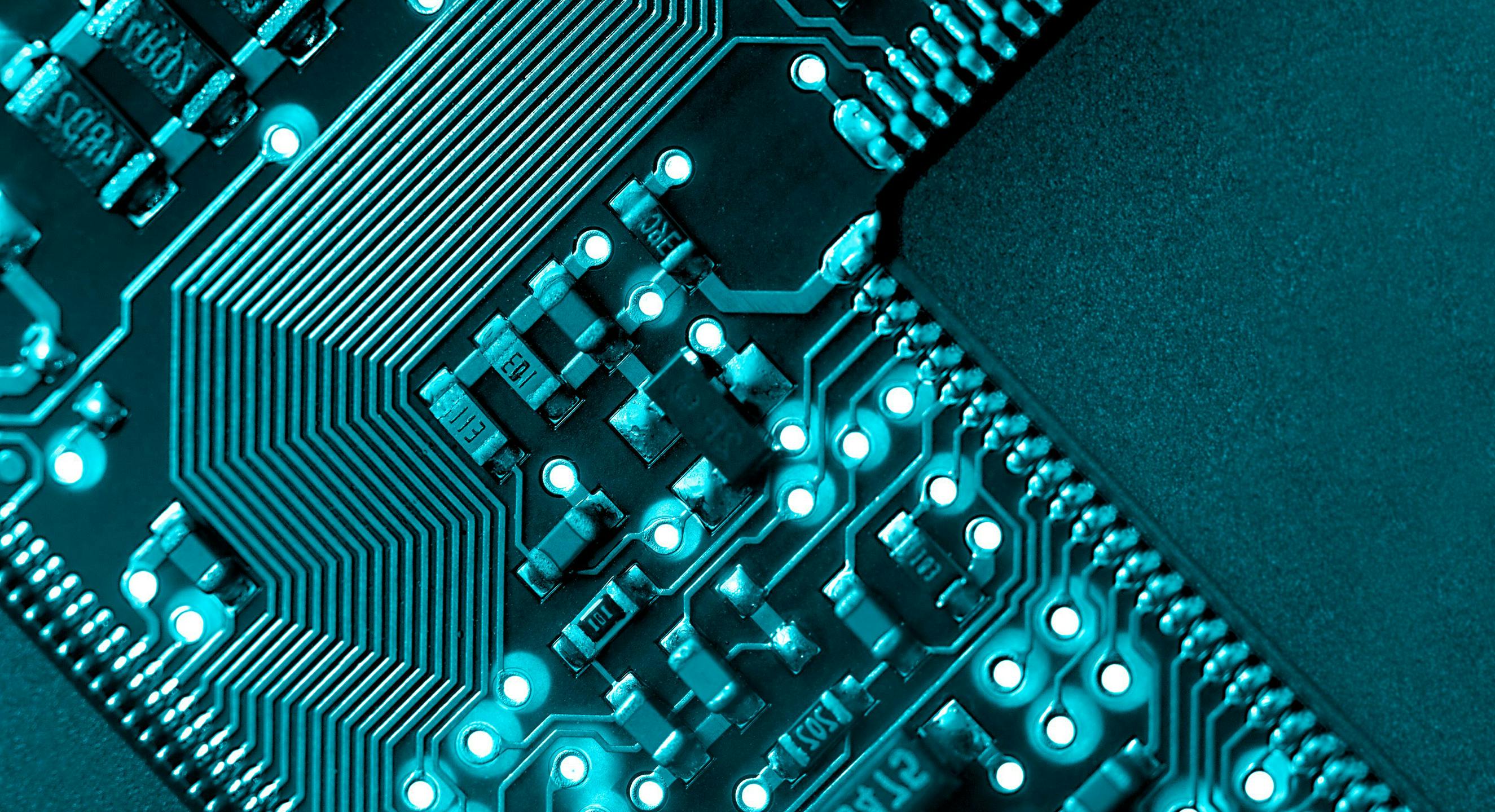

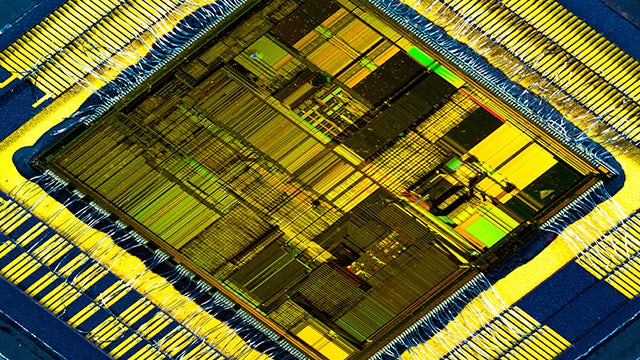

EDA trending technologies

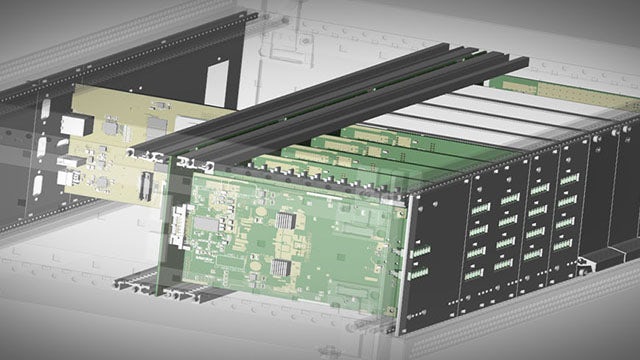

Explore our differentiating, holistic solutions for the technologies powering digitalization:

- 5G communications

- Sensor & IoT

- AI & ML

- High-performance computing & datacenter