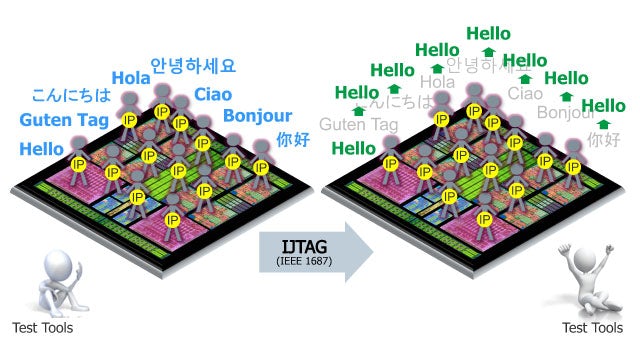

Why Tessent IJTAG?

The Tessent IJTAG product delivers comprehensive automation support for implementing the IEEE 1687 standard, providing plug-and-play IP test and instrumentation integration.

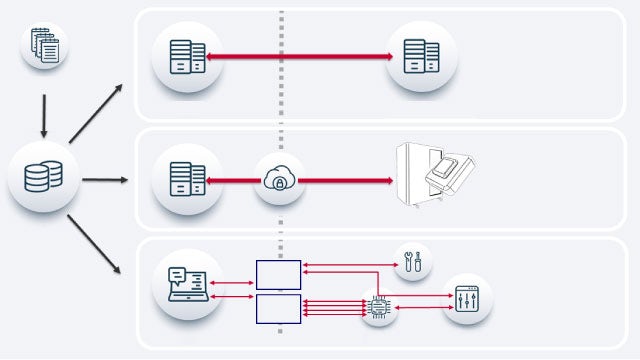

Create an IJTAG environment

Find and extract IJTAG Instrument Connectivity Language (ICL) network data from gate-level or RTL netlist, then create and insert the IJTAG network to gain uniform access and use of embedded IP.

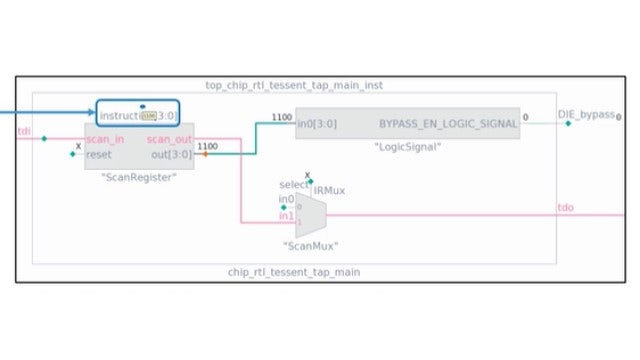

Verify IJTAG-compliant IP

Verify that IP is compliant with the IEEE 1687 standard and automatically create simulation testbenches.

Enable plug-and-play IP test

Gain uniform access to and use of embedded IP independent of the IP source and expand your options of embedded IP. Faster integration makes design schedules more predictable.