Veloce Apps

Veloce Apps address unique challenges in the SoC verification process.

Our portfolio of hardware-assisted verification applications includes software for completing power analysis, hybrid emulation, application of virtual platforms, DFT and Fault validation, system-level debugging and many more.

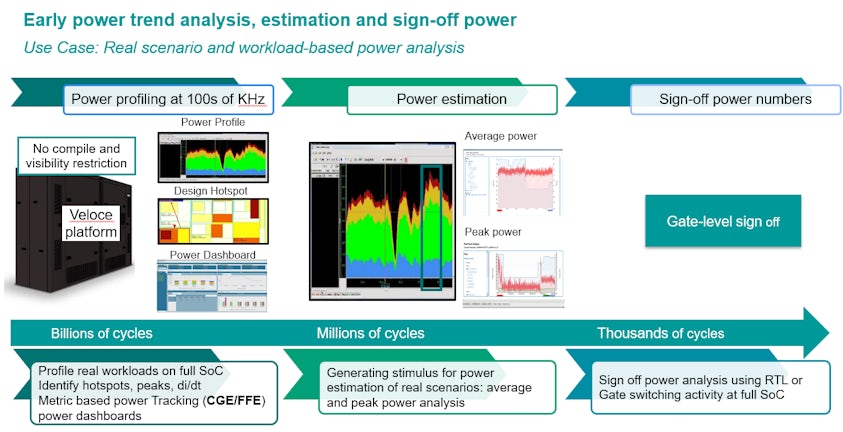

Veloce Power App

The Veloce Power solution enables early power analysis at the RTL level in 100s KHZ with detailed key power metrics for the entire duration of real workloads. In addition, it enables detecting key areas for further detail power estimation and producing stimulus for sign-off power tools.

The Veloce Power solution allows design teams to learn how each individual RTL block will behave in the full SoC context during real workload operations. This information can direct both RTL designers and software engineers to areas of interest in their designs and take actions to improve power efficiency. But as the design proceeds, attention shifts to more accurate power numbers for accurate power envelopes, thermal analysis, and packaging. Veloce power solution identifies the challenging areas for peak power and possible di/dt and generates stimulus for power-tools for further analysis.

Key Benefits/Features:

Veloce power solution key benefits:

- Generating power trend and power metrics for full SoC at 100s of KHZ

- With modular replay and the PowerStream App, early power analysis for the full SoC is achievable

- VDA and KPI will enable tracking across multi generations of the design and multiple design revisions

- Veloce's 100% visibility allows stimulus generation for power tools without any capacity impact

- Direct integration with Power Tools

Veloce Codelink App

Veloce Codelink provides users the ability to do SW debug and correlation to power profiles, performance, and HW events.

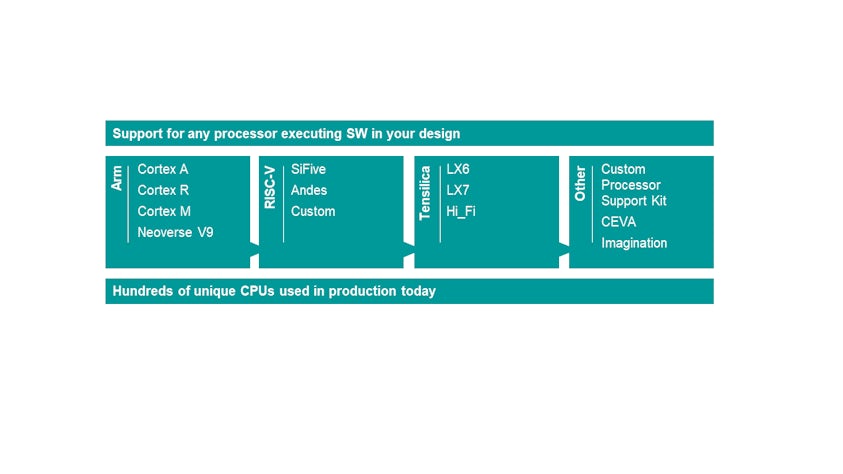

As part of the Veloce Ecosystem, Veloce Codelink helps ensure your project deadlines and milestones are met! With its powerful correlation engine, you gain visibility into whats happening in the HW & SW at the same time. Veloce Codelink's front end debugger, has all the necessary functionality a SW developer or a HW/SW verification team would expect, Have existing development flows? No problem. Veloce Codelink's support of the RSP-Protocol, which means your favorite front end debugger can be used in conjunction with Codelink replay functionality. Solutions for Arm, RISC-V, DSP's and custom processors means Veloce Codelink Roadmap is tightly aligned to our customers SW debug needs.

Key Benefits/Features:

- SW correlation to power profiles, performance, and HW debug

- Deterministic and non-intrusive replay based SW debug

- Offline debug at 100’s of MIPs speeds

- CPU Vendor Neutral

- SW code coverage

- SW performance profiling

- Cache Coherency debug

Veloce Fault App

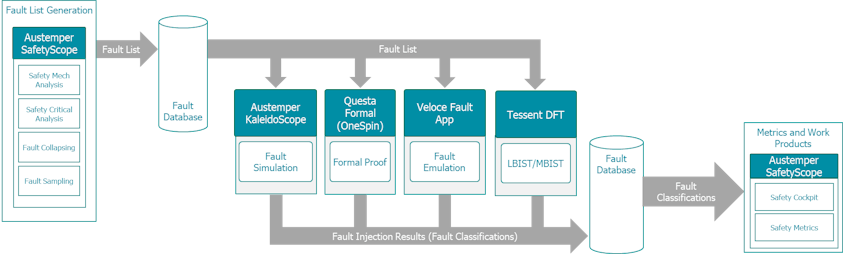

Veloce Fault App provides in conjunction with the Siemens EDA fault injection platform provides a seamlessly integrated and fully end to end ISO26262 certified fault injection solution.

The Veloce Fault App provides a high throughput emulation execution engine as part of Siemens EDA Fault Injection Platform. Using the Austemper SafetyScope structural analysis engine to generate an efficient fault list, Veloce Fault App executes stimulus and applies faults and finally categorizes the result. Final FMEDA metrics are calculated using Austemper SafetyScope. The entire tool chain centers around a shared FuSa database that allows for seamless data exchange.

Key Benefits/Features:

The Veloce Fault App key benefits include:

- Accelerate time to ISO26262 certification using common FuSa database

- Efficiently handle full SoC and full software stack

- Handle gate level netlist

- Several orders of magnitude acceleration

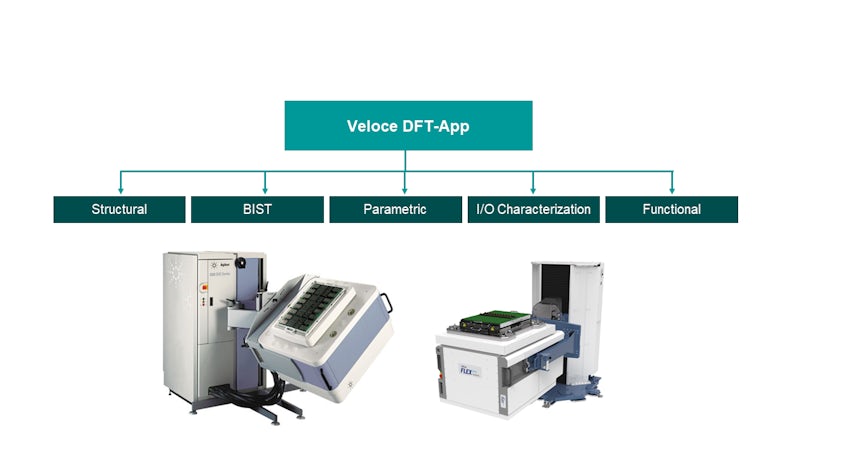

Veloce DFT App

Veloce DFT App provides a shift level approach to Design For Test pattern validation.

The Veloce DFT App is an emulation optimized, DFT pattern validation flow, that is orders of magnitude faster than traditional software simulation. The DFT App is compatible with all of the various types of test patterns that run on the ATE (Automated Test Equipment). The Veloce DFT App is fully compatible with the Veloce Fault App to accurately measure fault coverage or provide a functional fault grading metric. Used in conjunction with the Veloce Power App, power profiling and estimation of the the pattern to ensure a highly robust production program

Key Benefits/Features:

The Veloce DFT App key benefits include.

- Validate all patterns for correctness before shipping to production.

- Standard Test Interface Language (STIL)

- Support all patterns that run on ATE tester.

- DFT App is optimized for Emulation.

- Takes advantage of Co-Model streaming bandwidth

- Increase Fault Coverage through the use of the Veloce Fault App

- Power Profiling and estimation of patterns through the use of the Veloce Power App

- Reduce sim time “Days to Seconds"

Veloce Visualizer App

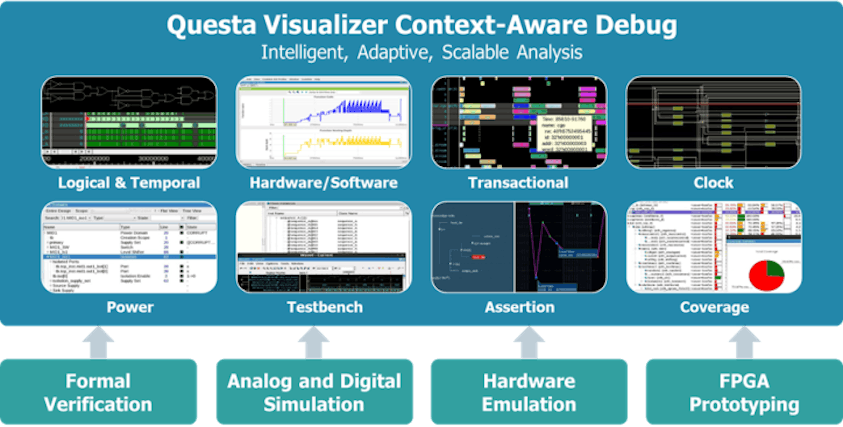

Visualizer is the 'Enterprise Verification Platform' debug solution.

According to 2022 Wilson research, design and verification engineers spend 46% of the project time debugging. Visualizer is the state-of-the-art debug platform suitable for today's functional verification challenges that are exponentially large and complex due to the presence of safety requirements, security requirements, hardware/software interactions, and complex system level integration. With the seamless merging of all the advanced debug features, and integration of UVM testbenches and Veloce emulation, Visualizer delivers a high performance debug for block level IP or full chip SoCs. Visualizer is built using latest technologies and is best suited to address the challenges of the future such as power streaming and analysis, code coverage Veloce Codelink SW debug, and protocol aware debug.

Key Benefits/Features:

- Common debug solution for all HAV platforms such as Veloce Strato, Veloce Primo, and Veloce proFPGA, and simulation

- Very fast, high capacity, and scalable to support large to very large designs.

- One debug engine for all debug needs RTL debug, GLE designs debug, testbench debug, SW debug, assertion, transactions, power analysis, and functional coverage.

- Visualizer's feature richness, intuitive windows, and rich color set make debug easy, reduce time and improve productivity.

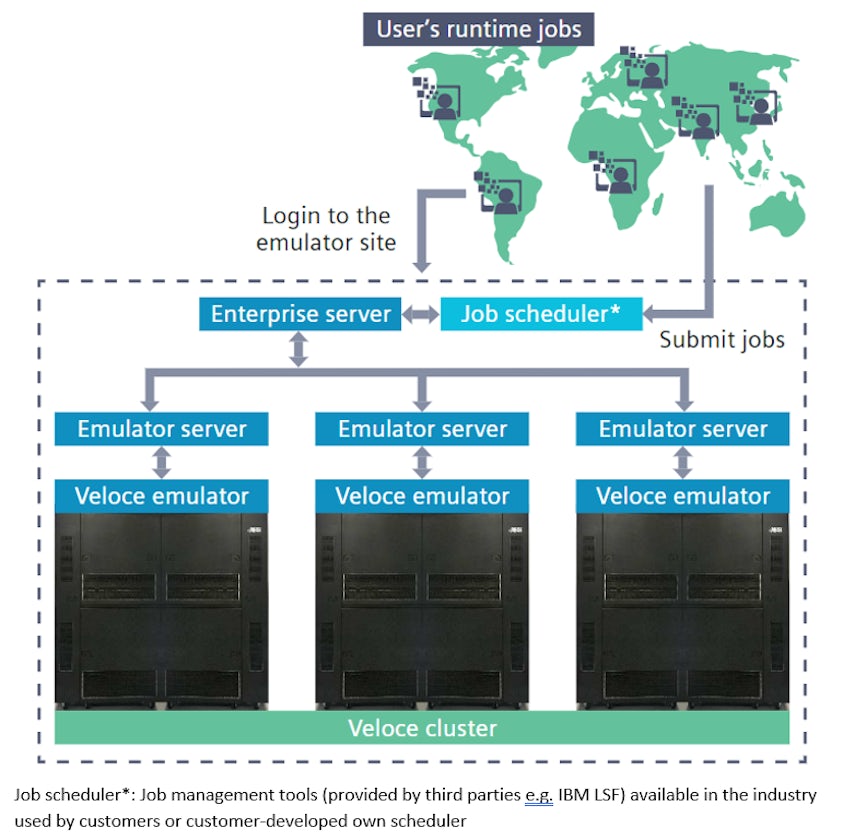

Veloce Enterprise Server (ES) App

Veloce ES App delivers a fully-integrated solution for complete, transparent access to emulation resources for helping customers dispatch their runtime jobs and maximize their emulator investments.

Without the Veloce ES App, users would need to have a deep understanding of the placement rules and algorithms used by the Veloce Emulator. Veloce ES App provide features like job preemption, large job starvation that can be invaluable for hardware design and testing teams.

ES App can also track and analyze hardware resources utilization.

Veloce HYCON App

These days, quicker turnaround times of silicon development is required, even if it is full custom. First pass silicon success is critical to enable faster go-to-market.

Siemens has a reference SoC platform with preconfigured HYBRID emulation environment, Veloce HYCON, that enables early software validation in a complex hybrid emulation environment for SoC designs pre-silicon.

Veloce HYCON is an evolution to traditional virtual platforms and hybrid emulation offerings.

Key Benefits:

- Enabling a software-driven design methodology for SOCs

- Provides a reference SW and HW Platform that customers can use on day one

- Applications and benchmarks optimize HW and SW together

- Provide customers with opportunity to produce full-system power estimates and optimization pre-silicon in the con

text of real application

- Allows for Multiple Use Models:

- Driver development and IP Validation

- SW Validation on a Hybrid SOC Platform

- Early Power and Performance Analysis in a complete SOC environment using real workloads

- Bridge the discontinuity between different levels of abstraction

Veloce HYCON stands for Hybrid and Configurable and it references the set of configurable reference platforms that customer can evolve to be their own custom HW/SW platform enabling

them to run benchmarks and SW workloads very early in the design cycle.

By executing software workloads, such as benchmarks and SW applications at the very early stage of the design cycle, Siemens is executing on the shift left promise and increasing the chance of first pass silicon success.

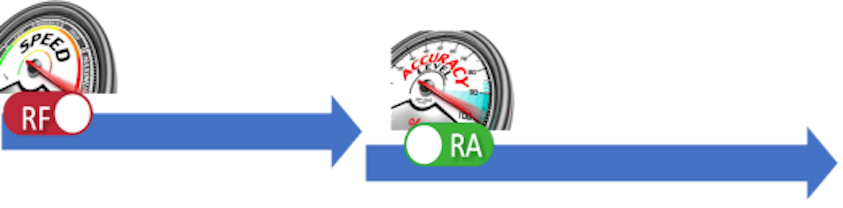

Performance When you want it and Accuracy when you need it

What makes Veloce HYCON unique is the ability to switch on the fly from a Virtual Environment to a full RTL environment at a specific point of SW execution that customers identify.

Veloce HYCON provides a harmonic combination of two different worlds: the virtual, software world and the hardware one. The target is to let users use and test their RTL without further requirements.

Rapid boot to home screen |

Rapid application test, driver development |

Virtual Peripherals with no SoC alteration |

Switch at customer area of interest |

Accurate bus, and cache performance metrics |

Power consumption and system level bottlenecks |

Continue to use Virtual Peripherals |

Veloce HYCON reference platforms ready from day 1 and capable of booting an operating system in seconds/minutes.

- Run Fast Run accurate; switches between the 2 worlds: Virtual and RTL on Emulator on the fly

- Ability to run Benchmarks on OS (Linux or Android) from day one

- Latest Linux/Android versions support

- Latest ARM Processor models support

- Native Support for QEMU or AFM

- Nowadays, quicker turnaround times of silicon development is required, even if it is full custom.

- First pass silicon success is critical to enable faster go-to-market

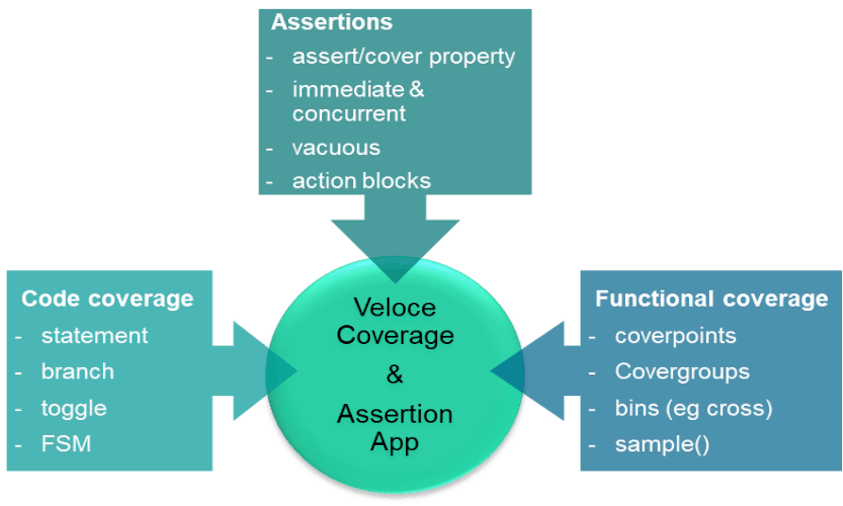

Veloce Coverage and Assertion App

Accelerate coverage closure, assertion-based coverage and debug to drive product quality and meet product schedules.

Metric-driven verification techniques with coverage and assertions are instrumental to quantify the extent of the design tested and to how it meets the required compliance and specification goals.

They are proven techniques to achieve first-pass silicon success by detecting issues early and reduce the risk of critical issues discovered in later phases of verification like post tape-out or in production.

Moreover, coverage and assertion techniques foster collaboration across different teams and provide a standardized way to communicate completeness while improving efficiency and cost-effectiveness in verification processes. Unifying coverage across the different verification engines provides a higher-level perspective of verification and validation sign-off assurance.

As hardware-assisted verification takes a leading role to validate a complex design and starting in parallel to simulation phase of developments, these techniques are indispensable to a wide set of hardware and software teams to ensure the quality of their design and software and verification environment are met.

Veloce Coverage and Assertion App is leverage by design teams for:

- Low power verification completeness across the power domains in SoCs.

- Stimulus guidance and stress-scenarios in the design to identify complex bugs early.

- Software teams to get feedback on the completeness of the design targeted and achieve validation closure.

- Compliance of standards such as DO-254

- Debug acceleration and better HAV utilization with assertions

Key Benefits/Features:

- Re-use coverage and assertions from simulation to achieve metric-driven verification goals.

- Highly configurable to dynamically control the coverage and assertion points during compile and run phases.

- Get feedback on the quality of extensive workloads that effectively cover the system features and stress scenarios.

- Fast coverage closure and efficient assertion-based debug for complex system level bugs.

- Comprehensive coverage analysis from stand-alone to cloud-based collaborative workflows.

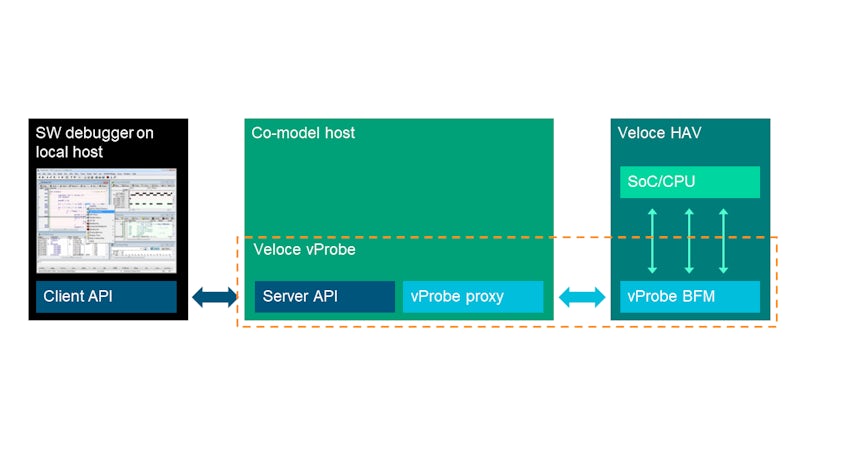

Veloce vProbe App

Veloce vProbe enables SW developers and HW/SW Validation teams with a consistent framework to shift-left firmware/embedded SW validation that is consistent with their post-si content validation.

Veloce vProbe App accelerates your SW development on HAV emulation and enterprise prototyping systems! By being able to develop, debug and execute your SW based workloads, vProbe is a key component in your SW based validation flow. Fully integrated with industry leading debuggers, Veloce Vprobe provides a consistent and congruent flow from emulation to prototyping to silicon. For HW verification teams, vProbe helps validate critical debug logic of your SoC ensuring your debug flow is ready for your post-si bring up.

Key Benefits/Features:

- Integration with third party SW debuggers

- TRACE32, Arm DS, CSAT, OpenOCD

- Connect to standard debug interfaces and trace ports

- JTAG, SWD, DAP-APB/ AHB/ AXI

- TPIU, trace port

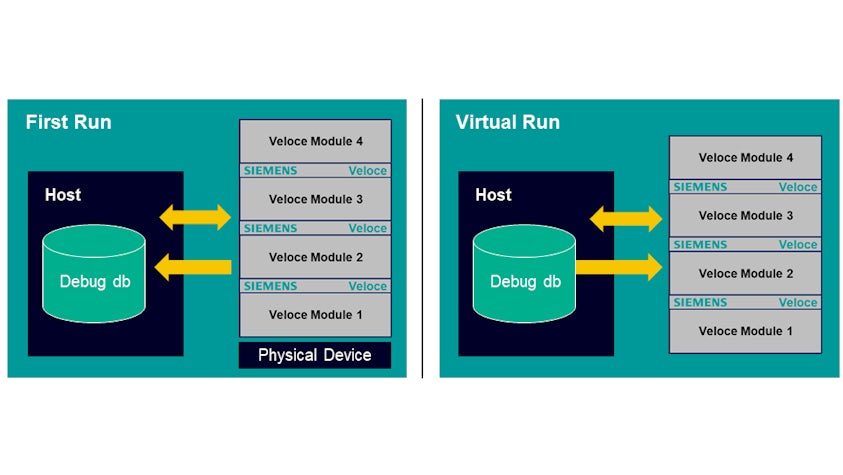

Veloce DE-ICE App

Repeatable debug for non-deterministic ICE environment.

Key Benefits/Features:

Veloce DE-ICE App overcomes ICE-based flow debug challenges.

- External dynamic targets can't be stopped arbitrarily.

- Limited flexibility and visibility per iteration.

- Randomness from one run to another could make bug disappear.

- Long and iterative debug cycles.

And opens the door to advanced debug techniques (Veloce Codelink App, Veloce Power App, Veloce Coverage App).

Veloce Vista App

Veloce Vista virtual prototype

The Veloce Vista virtual prototype allows software engineers to integrate, validate, analyze, and optimize their software against an early model of the hardware

As the complexity of embedded SOC grows, the need of early software development increases. Software-based methodologies involving virtual prototyping are helping to prove out designs earlier and incorporate hardware and software development. Modelling, simulating, and visualizing a hardware model’s functional behavior under real-world operating conditions are all phases of virtual prototyping development. These Functional Models combined, creates the Virtual prototype (VP).

Create TLM models, debug, optimize, and more

The Veloce Vista environment provides a simple way to create TLM platforms for SystemC structural code and link graphical symbols of individual TLM models to create customer’s own virtual platform. The Veloce Vista environment has also the ability to import external TLM models and add them to the vista model library.

Veloce Vista also enables software to be developed, integrated, and validated on a virtual representation of the hardware that has more benefits over prototyping boards

Veloce Vista for Architecture Exploration

- Architecture design and exploration

- Early assessment for functional and performance behavior of the HW system

- Visibility of key Hardware registers and attributes

- Support for large TLM models/cores and platforms

Veloce Vista for Software Validation

- Industry standard systemC TLM 2.0 Virtual prototype executable

- Validation of software against early virtual Hardware model

- Fast software execution speed

- Non-intrusive tracing, profiling, and SW coverage capability

- Intuitive Eclipse based software debug environment

- Large set of Embedded software analysis and debug capabilities

Veloce Vista environment offerings

- User Interface (UI)

- Platform creation

- pre-defined TLMs Library

- Creating TLM functions models with timing and power attributes

- Native TLM 2.0 block diagram for platform assembly

- Software development

- SW/HW analysis

- Debugging capabilities